Current Research Areas

Approches and Frameworks for Parallel Discrete-event and Cycle Based Simulation

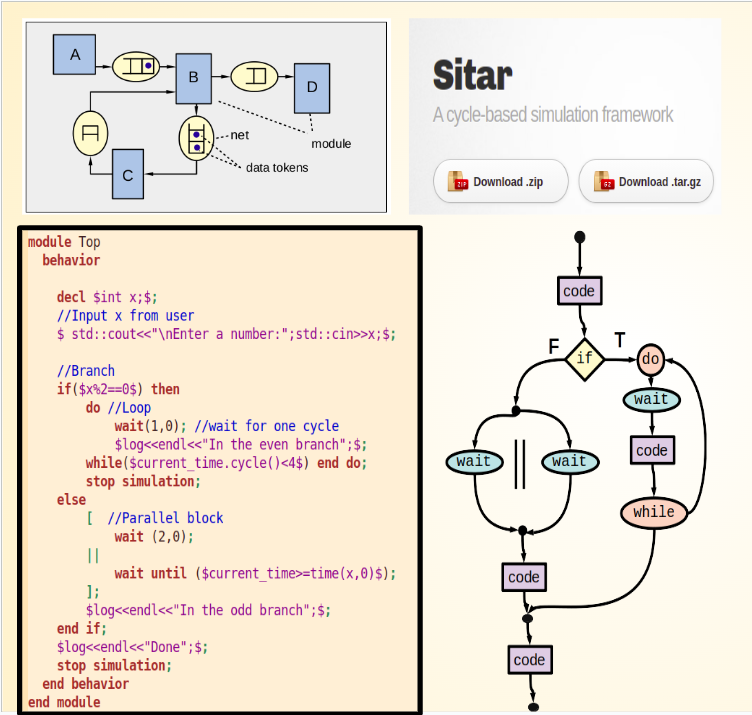

Sitar (Simulation Tool for Architectural Research)

[Project Webpage]

[Project GitHub Repo]

Sitar is a framework for modeling and parallel simulation of synchronous discrete-event systems (such as discrete time queues, computer networks and computer architectural models). It consists of a system description language and a cycle-based simulation kernel that uses a unique, easy-to-parallelize two-phase execution approach. The language allows a system to be described in a hierarchical manner as an interconnection of modules running concurrently. The behavior of each module can be described in an imperative manner using constructs such as time-delays, conditional wait statements, fork-join concurrency, and branch/loop constructs. C++ code can be embedded in a module description in a straightforward and well-defined manner. The sitar language parser has been written using Antlr V3. The simulation kernel is lightweight, consisting of a small set of C++ classes, and has been parallelized using OpenMP. Sitar received the best paper award at SIMULTECH2022 conference.

|

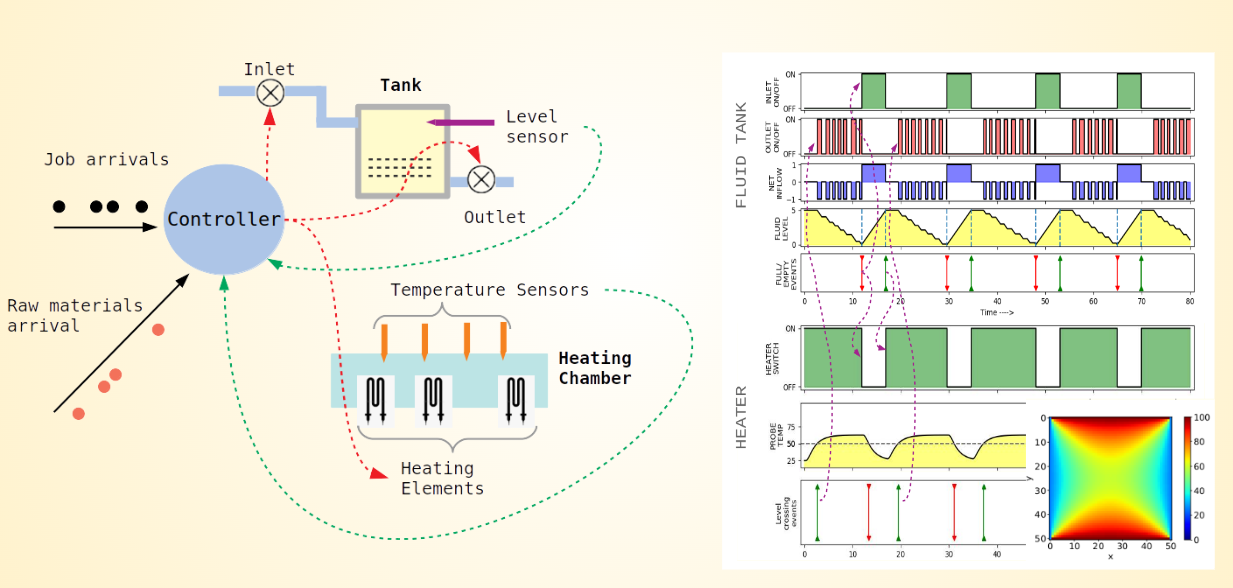

Approches for efficient simulation of Hybrid (mixed discrete-event and continuous) systems

We are developing efficient approaches and open frameworks for hybrid simulation of systems containing loosely coupled discrete-event and continuous processes (such as those in process simulation applications). A preliminary version of the framework is described in this paper.

|

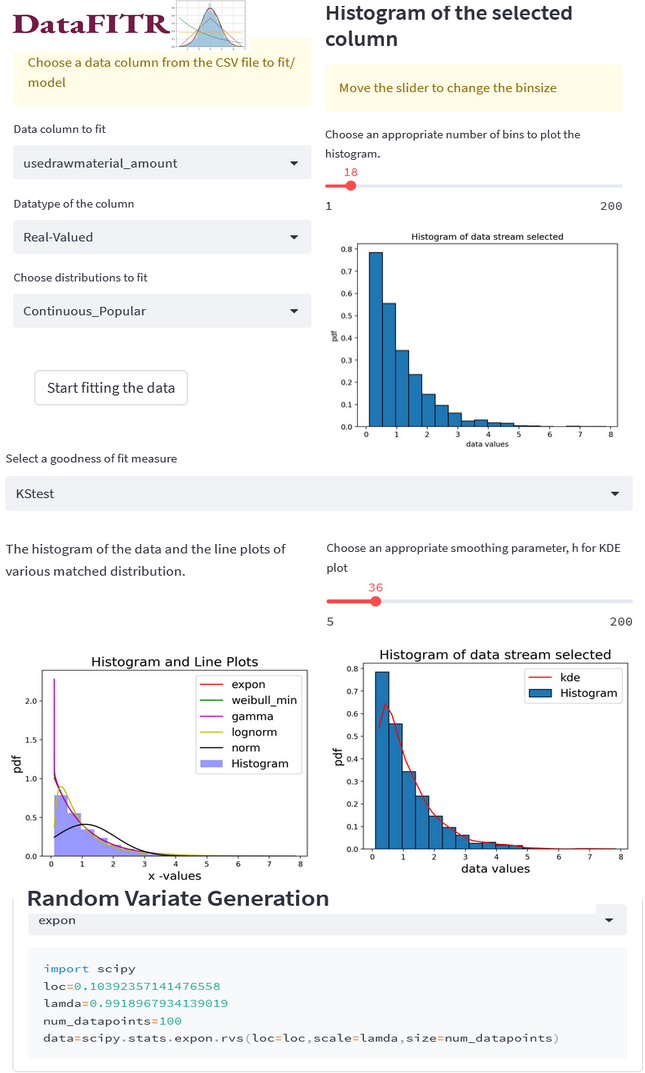

Approaches and Tools for Automated Model Generation

We are developing approaches and building tools for automated model generation.

As one component of this flow, we have built an open, cloud-hosted tool called DataFITR

for guided input modeling and random variate generation.

|

Open libraries for Simulation and Design exploration of Supply Chain Networks

We are developing an open Python library for the simulation of inventory and supply chain networks, coupled with meta-model based design exploration tool-sets. Preliminary work was published in Simultech 2023, and an extended abstract in SIGSIM PADS 2024.

Past Projects

Simulation-based Stochastic Optimization over Integer-valued Parameters in Queueing Networks and Computer System models

My PhD thesis proposed an embedding approach to convert the integer-valued parameters in a simulation model (such as queue or buffer capacities, number of servers and integer delays in a discrete-time model) into continuous parameters through a modification of the simulation model by introducing stochasticity in behavior. We showed that this yeilds a perfect interpolation of the long-run average performance measures. The embedding allows one to apply descent-based or other continuous optimizers directly over a simulation model for optimization over interger-valued and real-valued decision variables. This work was published in MASCOTS 2015 (for computer systems optimization) and ESM 2018 (for optimization of queueing networks).

IoT End-Point Simulation Framework for at-scale testing of middlewares and applications

This was a project at RBCCPS (IISc Bangalore) with the aim

of developing a scalable and flexible framework for the

simulation of the device layer in smart-city applications.

(August 2018 - January 2019)

Discrete-event modeling for Industrial IoT applications

As a part of an Energy-efficient assembly lines project at RBCCPS, the project

involved building simulation models of the assembly line for prediction, optimization

and real-time monitoring in an industrial Internet-of-Things framework. An open-source

simulator for an SMT-PCB assembly line with GUI support, developed as a part of this project

is available here.

PI: Prof. Rajesh Sundaresan, IISc Bangalore

(August 2017 - August 2018)

Development of Executable Simulation Models for the Ajit Processor

I developed detailed C-based functional and timing models of the memory subsystem components (caches, MMU, TLB, Main memory) and basic peripherals for the Ajit Processor (a Sparc-v8 based indiginous processor developed at IIT Bombay). I also worked on porting the Linux kernel to the Ajit processor platform by modifying the kernel entry code and writing basic device drivers.